Synchronous Counter Pada synchronous counter semua jalur input clock flip flop dihubungkan, sehingga setiap flip-flop mendapatkan pulsa clock secara bersamaan. Dengan konfigurasi menghubungkan semua input clock menjadi satu ini sychronous counter sering disebut dengan parallel counter.

Konfigurasi parallel pada syncronous counter ini memberikan keuntungan pada synchronous counter yaitu tidak terjadinya penundaan waktu propagasi (propagation delay). Synchronous counter juga memanfaatkan kondisi togle dari sebuah flip flop, pada synchronous conter flip-flop pertama akan selalu togle kemudian flip-flop selanjutnya akan togle pada saat output Q flip-flop sebelumnya berlogika HIGH. Untuk mendapatkan kondisi seperti itu pada synchronous counter ditambahkan gerbang AND untuk membaca logika output flip-flop sebelumnya. Rangkaian dasar sebuh synchronous counter 4 bit dapat dilihat pada gambar berikut. Rangkaian 4 Bit Synchronous Counter

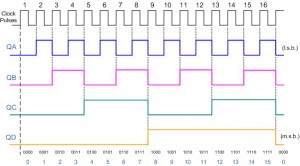

Dari rangkaian synchronous counter diatas untuk mendapatkan kondisi togle dari logika HIGH pada output flip-flop sebelumnya dipasang AND gate seperti terlihat pada gambar diatas. Dengan pemasangan AND sperti pada gambar diatas maka : 1.Flip-flop pertama akan togle setiap input clock diberikan. 2.Flip-flop kedua akan togle hanya pada saat output 3.flip-flop pertama (Q0) dalam kondisi HIGH. Flip-flop ketiga hanya akan togle apabila output flip-flop pertama (Q0) dan output fli-flop kedua (Q1) dalam kondisi HIGH. 4.Flip-flop keempat hanya akan togle pada saat output flip-flop pertama (Q0), output flip-flop kedua (Q1) dan output fli-flop ketiga (Q2) dalam kondisi HIGH. Timing Diagram Synchronous Counter

Output dari masing-masig flip-flop (Q0, Q1, Q2 dan Q3) menunjukan prose penghitungan (counter) naik dari setiap pemberian pulsa clock pada input rangkaian. Dengan output seperti ini maka rangkaian counter diatas dinamakan sebagai pengitung naik (Synchronous Up Counter).

Dari gambar rangkaian dan timing diagram diatas maka dari synchronous counter dapat diambil beberapa kesimpulan sebagai berikut.

Keunggulan Dari Synchronous Counter

Cukup sekian keterangan Synchronous Counter semoga bermanfaat.

Dari gambar rangkaian dan timing diagram diatas maka dari synchronous counter dapat diambil beberapa kesimpulan sebagai berikut.

- Synchronous counter dibuat dengan togle flip-flop yang dapat disusun dari JK-FF maupun D-FF.

- Disebut sebagai synchronous counter karena semua flip-flop mendapat input secara bersamaan dalam setiap pulsa clock diberikan.

- Setiap output dai masing-masing flip-flop yang digunakan akan memberikan output secara bersamaan pada saat pulsa clock diberikan.

- Synchronous counter disebut juga sebagai paralel counter karena semua input clock dijadikan satu dan akan memberikan output secara bersamaan dalam setiap pulsa clock.

- Proses penghitungan secara berurutan terjadi karena penambahan gerbag logika untuk memastikan output flip-flop sebelumya sudah belogika HIGH dahulu.

Keunggulan Dari Synchronous Counter

- Mudah didesain untuk keperluan aplikasi yang lebih kompleks.

- Tidak terjadi propagation delay karena semua flip-flop mendapat input clock secara bersamaan.

- Memiliki kecepatan yang lebih baik dalam aplikasi counter atau rangkaian yang lebih besar.

Cukup sekian keterangan Synchronous Counter semoga bermanfaat.

Komentar

Posting Komentar